# 32-bit General Purpose I/O Interface IC

# PIX132 User's Manual

2005-9-08 Ver. 1.0 2012-2-20 Ver. 2.1

## Introduction

Before using the PIX132, please read this manual thoroughly to ensure correct usage according to specifications such as signal voltage, signal timing, and operational parameter values.

In general, semiconductor products can malfunction or fail to function. Therefore, when incorporating this IC into a system, ensure that a safety system is designed to prevent injury or damage to property caused by any malfunctioning of this IC.

The PIX132 is designed for application to general electronic devices such as industrial automation and robotics, measurement instruments, computers, office equipment, household electrical goods, and so on. This IC is not intended for use in high-performance, high-reliability equipment where failure or malfunctioning may directly cause death or injuries (atomic energy control equipment, aerospace equipment, transportation equipment, medical equipment and various safety devices) and operations for such uses cannot be guaranteed. The customer shall be solely responsible for the use of this IC in any such high-performance and high-reliability equipment.

# Notes on independent mode:

Before using in independent mode, make sure that INTN/TEST signals (14 pins) are short-circuited to GND. Keeping them open can cause malfunction due to running internal test circuits on this IC.

| 1.   | Outline                                                                           | 6  |

|------|-----------------------------------------------------------------------------------|----|

| 2.   | How to Operate PIX132                                                             | 12 |

| 2.1. | General Input/Output Operation                                                    | 12 |

| 2.2. | Simultaneous Input Latch                                                          | 12 |

| 2.3. | Input Transition Trapping Function                                                | 13 |

| 2.4. | Simultaneous Output Set                                                           | 14 |

| 2.5. | Bit Control Output                                                                | 14 |

| 2.6. | Built-in Timer                                                                    | 15 |

| 2.7. | Interrupt Generation                                                              | 15 |

| 2.8. | Status at Reset                                                                   | 15 |

| 3.   | Pin Assignments and Signal Description                                            | 16 |

| 3.1. | Pin Assignments                                                                   | 16 |

| 3.2. | Signal Description                                                                | 17 |

| 3.3. | Input/ Output Circuit                                                             | 19 |

| 3.4. | Notes for Design Circuitry                                                        | 19 |

| 4.   | Register                                                                          | 20 |

| 4.1. | WR0 Register Command Execution / Bit Control Output: 0                            | 20 |

| 4.2. | WR1 Register Bit Control Output: 1                                                | 21 |

| 4.3. | WR2,3 Register Data Writing                                                       | 21 |

| 4.4. | WR4,5,6,7 Register Port Output Value Setting                                      | 22 |

| 4.5. | RR1 Register Display of Interrupt Request Factor                                  | 22 |

| 4.6. | RR2,3 Register Display of Reading Data                                            | 23 |

| 4.7. | RR4,5,6,7 Register Display of Real-time Input/Latch Input/Output/Input Transition | 23 |

| 5.   | Commands                                                                          | 25 |

| 5.1. | Commands for Data Writing                                                         | 26 |

| 5.1.1. Input/Output Designation and Logical Setting                                                                                                  | 26       |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.1.2. Input Filter Designation                                                                                                                      | 26       |

| 5.1.3. Filter Time Constant Setting                                                                                                                  | 27       |

| 5.1.4. Timer Value Setting                                                                                                                           | 28       |

| 5.1.5. PAB Input Transition Enabling Setting                                                                                                         | 29       |

| 5.1.6. PCD Input Transition Enabling Setting                                                                                                         | 29       |

| 5.1.7. PAB Input Transition Direction Setting                                                                                                        | 29       |

| 5.1.8. PCD Input Transition Direction Setting                                                                                                        | 30       |

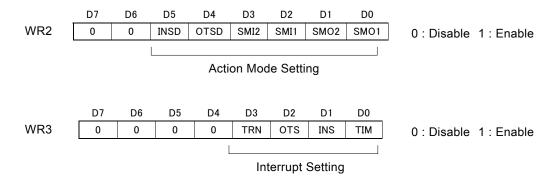

| 5.1.9. Action Mode / Interrupt Setting                                                                                                               | 30       |

| 5.2. Commands for Reading Data                                                                                                                       | 33       |

| 5.2.1. Reading Setting Data                                                                                                                          | 33       |

| 5.2.2. Read Register Display Status Reading                                                                                                          | 33       |

| 5.2.3. Activated Timer Value Reading                                                                                                                 | 34       |

| 5.3. Other Commands                                                                                                                                  | 35       |

| 5.3.1. Timer Single Activation                                                                                                                       | 35       |

| 5.3.2. Timer Continuous Activation                                                                                                                   | 35       |

| 5.3.3. Timer Stop                                                                                                                                    | 35       |

| 5.3.4. Timer Cycle Stop                                                                                                                              | 35       |

| 5.3.5. Input Transition Information Clear                                                                                                            | 35       |

| <ul><li>5.3.6. Read Register Display Selecting 1 Real-time Input + Output</li><li>5.3.7. Read Register Display Selecting 2 Real-time Input</li></ul> | 36<br>36 |

| 5.3.8. Read Register Display Selecting 3 Latch Input                                                                                                 | 36       |

| 5.3.9. Read Register Display Selecting 4 Output                                                                                                      | 36       |

| 5.3.10. Read Register Display Selecting 5 Input Transition                                                                                           | 37       |

| 5.3.11. Simultaneous Input Latch                                                                                                                     | 37       |

| 5.3.12. Simultaneous Output Set                                                                                                                      | 37       |

| <ul><li>6. Independent Mode</li><li>7. Examples</li></ul>                                                                                            | 38<br>40 |

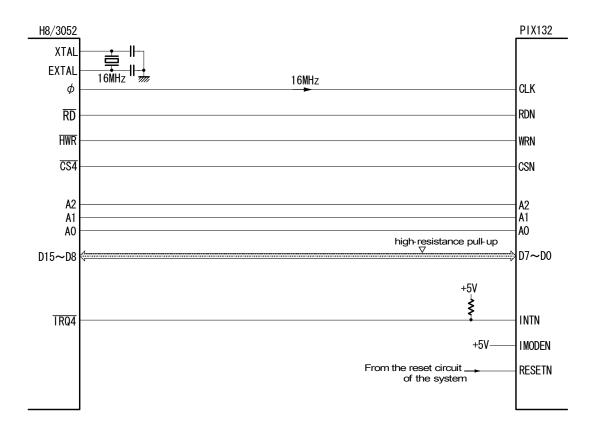

| 7.1. Connection Example for the CPU                                                                                                                  | 40       |

| 7.2. Example Program                                                                                                                                 | 40       |

| 1.E. Example 1.10g. and                                                                                                                              |          |

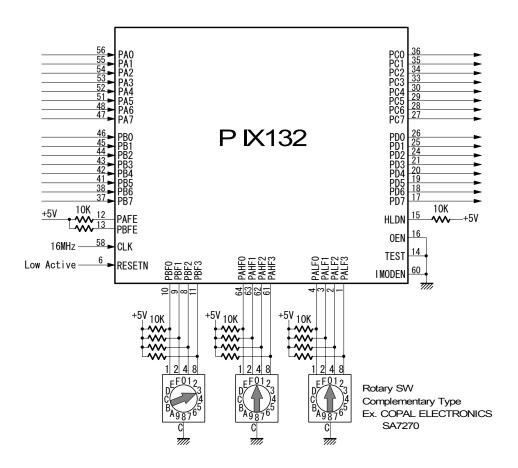

| 7.3. Connection Example for Independent Mode                                                                                                         | 43       |

| 8. Electrical Characteristics                                                                                                                        | 44       |

| 8.1. DC Characteristics                                                                                                                              | 44       |

| 8.2. AC Characteristics                                                                                                                              | 45       |

| 8.2.1. Measuring Condition                                                                                                                           | 45       |

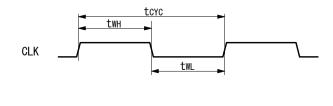

| 8.2.2. Clock                                                                                                                                         | 45       |

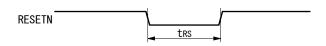

| 8.2.3. Reset Signal Width                                                                                                                            | 45       |

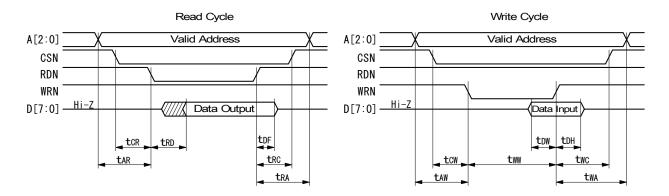

| 8.2.4. CPU Read/ Write Cycle                                                                                                                         | 46       |

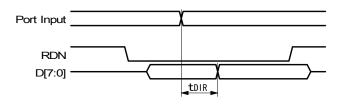

| 8.2.5. Port Input Delay Time                                                                                                                         | 47       |

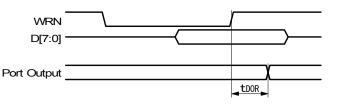

| 8.2.6. Port Output Delay Time                                                                                                                        | 47       |

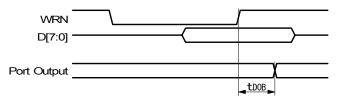

| 8.2.7. Bit Control Output Delay Time                                                                                                                 | 47       |

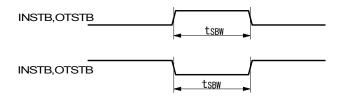

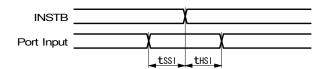

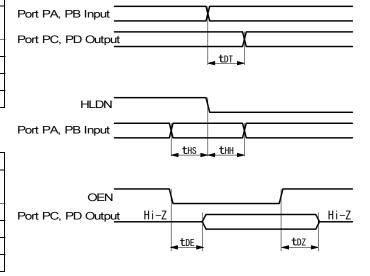

| 8.2.8. Strobe Signal Width 8.2.9. Simultaneous Input Latch Timing                                                                                    | 47<br>48 |

| U.Z.J. OHHURANGUUS INPUL LARUH HIIIIIIY                                                                                                              |          |

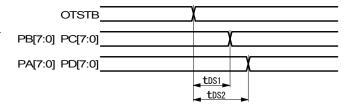

| 8.2.10. Simultaneous Output Set Delay Time                                                                                                           | 48       |

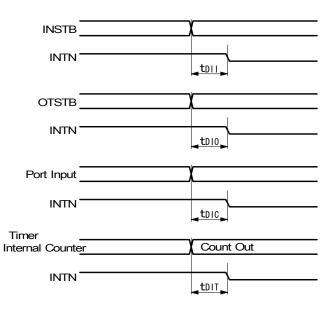

| 8.2.11 Interrupt De 8.2.12. Delay Time | elay Time<br>in Independent Mode          | 49<br>49 |

|----------------------------------------|-------------------------------------------|----------|

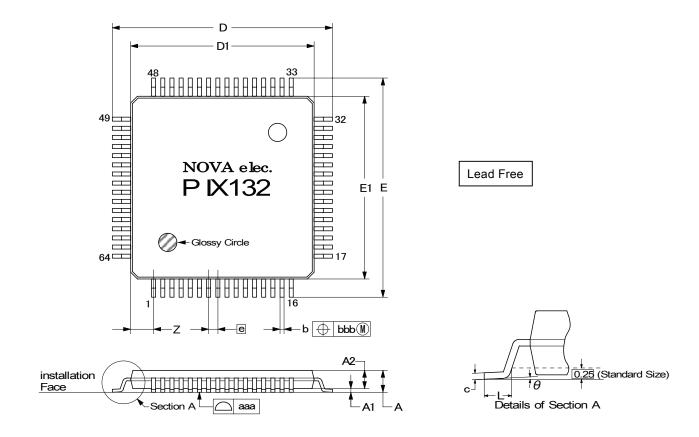

| 9. Package                             | Dimensions                                | 50       |

| 10.PIX132 S                            | Storage and Recommended Installation      |          |

| Conditions                             |                                           | 52       |

| 10.1 Storage of th                     | nis IC                                    | 52       |

| 10.2 Standard Inst                     | tallation Conditions by Soldering Iron    | 52       |

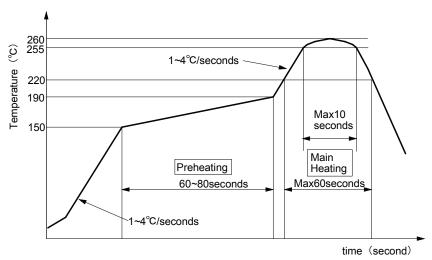

| 10.3 Standard Inst                     | tallation Conditions by Solder Reflow     | 52       |

| Appendix A                             | Clock Frequency Conversion Formula        | 53       |

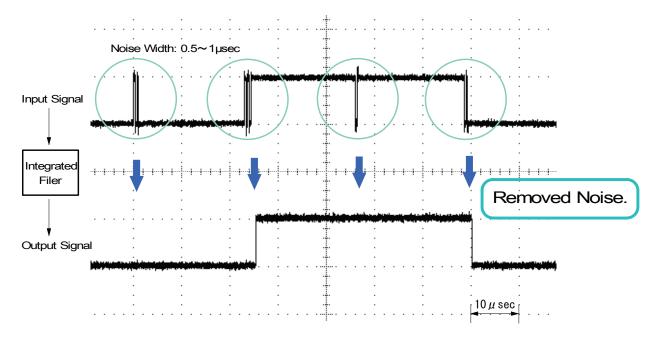

| Appendix B                             | Noise Removal of Built-in Integral Filter | 54       |

# 1. Outline

PIX132 is a 32-bit general purpose I/O interface IC equipped with a built-in digital integral filter. It can independently configure input/output, input logic or filter time constant every 4-bit port. PIX132 provides various functions for output like bit control output and simultaneous output set, with a single power supply within the 3.0 to 5.5V range so as to function on both 5V and 3.3V systems.

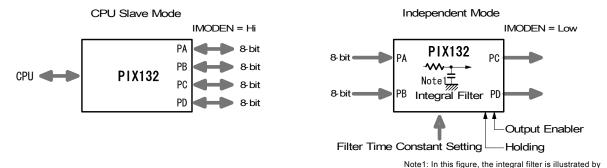

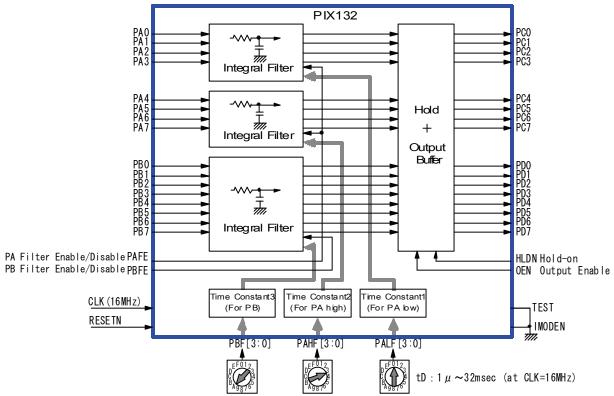

PIX132 has two operational modes as shown in Fig.1.1. The first is the CPU slave mode used in conjunction with the CPU bus and the other is the independent mode where sixteen input ports are output through a built-in integral filter. When the IMODEN input signal is set to Hi, the PIX132 operates in slave mode and when set to Low, it operates in independent mode.

CR, but the signal is digitally processed in the IC. Fig.1.1 Two Operational Modes of PIX132

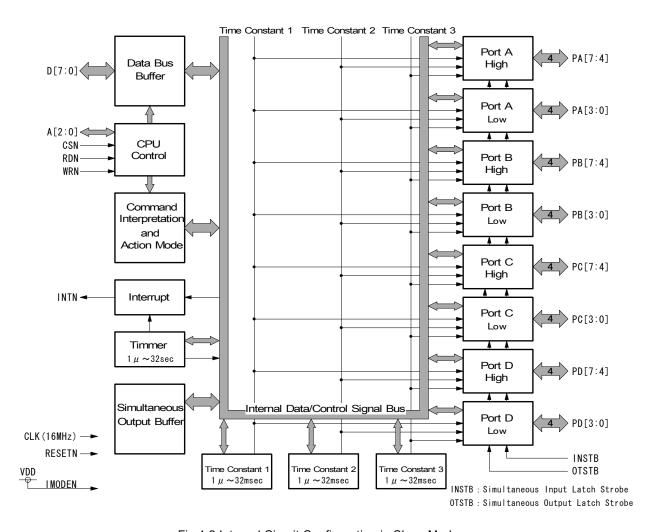

Fig. 1.2 shows the functional configuration in the IC when used in slave mode.

Fig.1.2 Internal Circuit Configuration in Slave Mode

The PIX132 has 32 general purpose I/O signals, consisting of four 8-bit ports: Port A, Port B, Port C and Port D. Each 8-bit port is divided into upper and lower 4-bit ports and these can be independently configured for input/output, selection of filter time constant or input logic. The input signal is equipped with a built-in integral filter and each filter can select one time constant from three types.

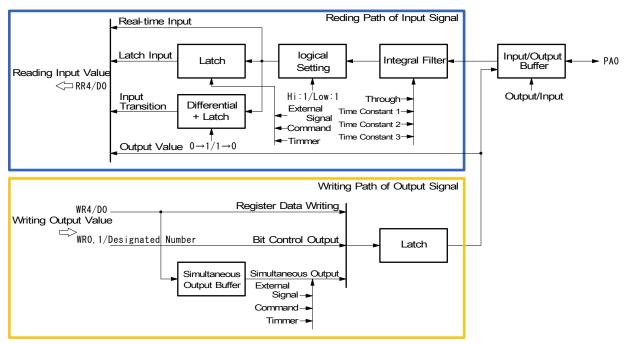

Fig.1.3 shows the reading and writing flow of input/output signals, taking as an example a PA0 signal, one of the 32-bit I/O signals.

Fig. 1.3 Reading and Writing path of input/output signals

#### Reading Flow of the Input Signal

As shown in Fig.1.3, first an input signal passes through an integral filter; a signal can be passed through without the filter. When passing through the filter, the user can select one time constant from types 1, 2 and 3 which are each configurable for delay time from 1  $\mu$  sec to 32msec. Every 4-bit port can be specified as to which time constant to be used. The signal passing the filter is set to the logical level, where its level can be specified as Hi or Low to 1.

The CPU can attain the following information regarding logical input values:

- Real-time Input Information about real-time input signals.

- 2 Latch Input Information about all inputs which are latched simultaneously by external latch strobe signals, command writing from the CPU or the time-out of the timer.

- 3 Input Transition Information about the transition of the specified input from 0 to 1 or 1 to 0.

The CPU reads these information inputs from RR4 to 7 registers. RR4~7 registers are 8-bit configurations respectively, corresponding to RR4:PA[7:0], RR5:PB[7:0], RR6:PC[7:0], RR7:PD[7:0]. RR4~7 registers display not only with real-time inputs but also latch inputs and input transition. These information inputs are switched by the command E5~E9h.

# **Output Signal Setting**

As shown in Fig.1.3, output signals can be set by the following three ways when each I/O port is designated for output.

- ① Register Data Writing Writing output data in WR4, 5, 6 and 7 registers, output is set by the 8-bit ports, PA, PB, PC and PD.

- ② Bit Control Output Writing the assigned number corresponding to the output signal, output is set by a single bit.

- Simultaneous Output Writing output data in WR4, 5, 6 and 7 registers in advance, all outputs are simultaneously set at the timing of external strobe signal, command writing from the CPU and time-out of the timer.

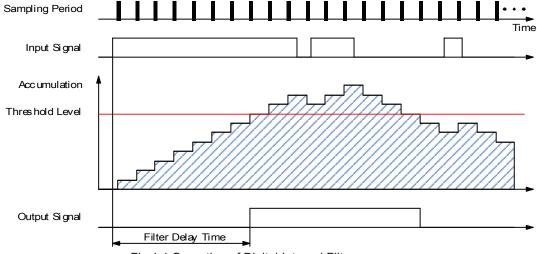

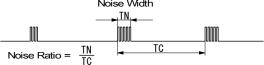

## Digital Integral Filter

The PIX132 is equipped with a digital integral filter for each input signal of port PA $\sim$ PD. This filter takes samplings of input signal level at the designated period, and then outputs the accumulation of value to the back. It provides the function that removes impulse noise, which is almost the same performance as the integral filter composed of RC (Resistance, Capacitor) elements (See appendix B.) and can reduce the space on the circuit board for RC elements and cost. In addition, once the RC elements are soldered, the time constant will be fixed. On the other hand, the built-in integral filter of this IC can alter delay time from 1  $\mu$  sec to 32msec (at CLK=16MHz) any time, depending on the circumstances of the noise.

Fig.1.4 Operation of Digital Integral Filter

## Simultaneous Input Latch

This function is to latch all the input signals of port PA~PD simultaneously in the following three ways. The user can specify which way is to be used by action mode setting command.

① Strobe Signal Latch at the rising/falling edge of the external signal(INSTB). The rising or falling can be selected by action mode setting command.

2 Command Latch by writing the command EAh from CPU to WR0 register.

3 Timer Latch at the time-out of the timer.

The latched input information can be read out from RR4~7 registers. However, when RR4~7 registers are displaying other information, the latched input information can be read out after writing the command E7h.

## Input Transition Trapping Function

This function is to trap the transition of input signals. The transition of the input value from 0 to 1 or from 1 to 0 can be trapped concerning specified inputs. It is effective to monitor the rare transition of a signal or unexpected impulse noise that mixes with a signal. The user can specify the signal and the direction of the transition (0 to 1/1 to 0) by the bit.

Fig. 1.5 Operation of Input Transition Trapping

The input transition information can be read out from RR4~7 registers. However, when RR4~7 registers are displaying other information, the input transition information can be read out after writing the command E9h. Once input transition information is read out, it will be cleared.

This function is activated by clock (CLK) synchronization. If the input transition occurs in less time than CLK cycle, it may fail to be trapped.

### Simultaneous Output Set

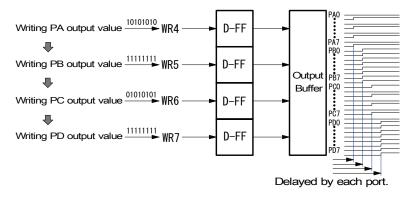

Normally writing the signal value (0:Low and 1:Hi) designated for output to WR4, 5, 6 and 7 registers will be set to each 8-bit output port. Thus, as shown in Fig.1.6, when the user tries to set all of the ports PA~PD in the usual way, the output set is delayed by each port, because a time difference occurs at the time of writing to each port, PA~PD from the CPU.

Fig.1.6 Normal Output Set

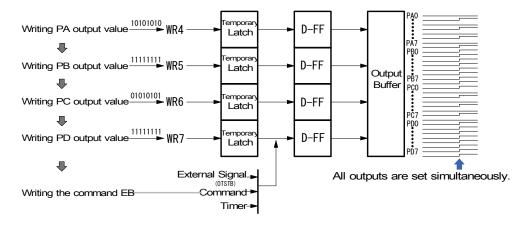

This IC can perform to simultaneously set all of the output signals of each port, PA~PD by setting action mode. As shown in Fig.1.7, if the simultaneous output mode is set, then the output data of port PA, which is written in WR4 register, is temporarily latched and not outputted to port PA yet. Also values written in WR5, 6 and 7 registers are not reflected immediately and they are temporarily latched.

Fig.1.7 Simultaneous Output Set

To output data simultaneously from output ports after writing output values in WR4, 5, 6 and 7 registers, there are the following three ways:

① Strobe Signal Output at the rising/falling edge of the external signals (OTSTB). The rising or falling can be selected by action mode setting command.

2 Command Output by writing the command EBh from CPU to WR0 register.

3 Timer Output at the time-out of the timer.

[Note] In a customer system, when the user tries to control switching on/off of a large current simultaneously with this function, it is necessary to take preventive measures that minimize the voltage fluctuation of GND/Power or Cross-talk between the signals which are generated by simultaneous switching of a large current.

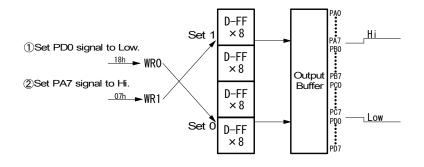

### Bit Control Output

This function is to set an output signal by a single bit. In the ususal way, the output set is performed by writing to WR4, 5, 6 and 7 registers, so that signals are set to each 8-bit port. Therefore, when the user tries to set one specified output signal to Hi or Low level, the user first must set the specified bit of 8-bit output data to 1OR or 0AND, then write it to the register. This IC does not need such a burdensome operation. As shown in Fig.1.8, to set one specified signal to Low level, write the designation number for the signal to WR0 register, then the signal will be set to Low or write the designation numbert for the signal to WR1 register, then the signal will be set to Hi.

Fig.1.8 Example of Bit Control Output

## Interrupt Generation

The interrupt signal can be generated by input transition, external strobe and the timer.

Input Transition Interrupt can be generated at the transition of the specified input signal

from 0 to 1 or 1 to 0 (selectable) concerning all the input signals.

External Strobe Interrupt can be generated at the transition of external strobe signal

(INSTB) for simultaneous input latch or external strobe signal (OTSTB) for simultaneous output set. The CPU can efficiently control because of no

need to wait for these signals.

Timer Timer can be configured within the range from  $1 \mu$  sec to 32sec.

Interrupt can be generated at the time-out of the timer.

### Reading Setting Value

Configuration such as input/output settings, logical settings, filter settings, output data or all setting data set by the CPU can be read out. The current setting data can be read any time so that the CPU does not need to separately keep such output data even when bit control output is performed.

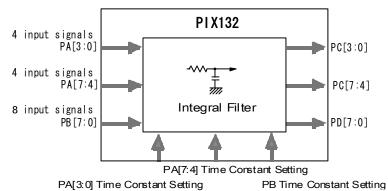

## **Independent Mode Operation**

Independent mode is the operation mode that mainly uses only the integral filter function of this IC and does not connect this IC to the CPU bus. Fixed 16 bit inputs are output to fixed output signals through the integral filter.

The filter time constant can be set to 4-bit of PA[3:0], 4-bit of PA[7:4] and 8-bit of PB[7:0] respectively. And each delay time of the time constants can be externally designated within the range from 1  $\mu$  sec to 32msec.

No

Note1: In this figure, the integral filter is illustrated by CR, but the signal is digitally processed in the IC.

Fig.1.9 PIX132 Independent Mode

In addition, the signal for filter enable/disable, output signal holding and output signal enabling (enable/high impedance) are prepared.

# 2. How to Operate PIX132

## 2.1. General Input/Output Operation

This chapter shows the user how to operate PIX132 in slave mode which is used in conjunction with the CPU bus. PIX132 has four 8-bit ports, port PA, PB, PC and PD. Each 8-bit port is divided into upper and lower 4-bit ports and these 4-bit ports can be independently configured input/output, input logic or filter. The operating procedures, such as configuration of each port, input reading and output set, are shown as follows:

#### (1) Input/Output and Input Logical Setting

Configure each port whether to be used as input or output. When used as input, input logic is also configured either Hi or Low to 1.

|       | Reference                      | Page |

|-------|--------------------------------|------|

| 5.1   | Commands for Data Writing      | 26   |

| 5.1.1 | Input/Output and Input Logical | 26   |

|       | Setting                        |      |

## (2) Input Filter Designation

Concerning the port configured as input, the user specifies whether to pass through the integral filter or not. In the case of using the integral filter, the user can select one time constant from three types.

|       | Reference                    | Page |

|-------|------------------------------|------|

| 5.1   | Commands for Data Writing    | 26   |

| 5.1.2 | Filter Time Constant Setting | 27   |

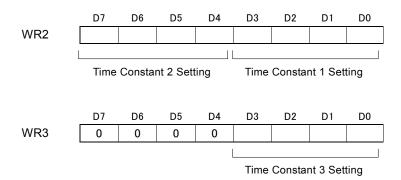

#### (3) Filter Time Constant Setting

Configure the time constant of the integral filter of this IC. There are three types of time constants 1, 2 and 3. Each time constant can configure the delay time within the range from 1  $\mu$  sec to 32msec.

|   |       | Reference                    | Page |

|---|-------|------------------------------|------|

| ٠ | 5.1   | Commands for Data Writing    | 26   |

|   | 5.1.3 | Filter Time Constant Setting | 27   |

### (4) Input Reading

Switch RR4, 5, 6 and 7 registers to a display "Real-Time Input" by writing Read Register Display Selecting 2 command (E6h).

Reading RR4, 5, 6 and 7 registers corresponding to each port, the current input signal status (the input value configured logical setting after passing the filter) is available.

| Reference                                  | Page |

|--------------------------------------------|------|

| 5.3.7 Read Register Display<br>Selecting 2 | 36   |

| 4.7 RR4,5,6,7 Register                     | 23   |

## (5) Output Set

When the port is configured as output, output signals can be set by writing the data in WR4, 5, 6 and 7 registers.

To read out the output data currently set, write Read Register Display Selecting 4 command (E8h) and then switch RR4, 5, 6 and 7 registers to a display "Output".

|   | Reference                   | Page |

|---|-----------------------------|------|

|   | 4.4 WR4,5,6,7 Register      | 22   |

|   | 5.3.9 Read Register Display | 36   |

|   | Selecting 4                 | 30   |

| , | 4.7 RR4,5,6,7 Register      | 23   |

|   |                             |      |

# 2.2. Simultaneous Input Latch

This function is to latch all the input signals of port PA~PD simultaneously. To latch simultaneously, there are three ways: strobe signal, commands and the timer. The user can specify which way is to be used by action mode/interrupt setting command.

#### (1) Latch by Strobe Signal or Commands

To perform simultaneous input latch by strobe signal (INSTB) or commands, set 1 to WR2/D2 bit by action mode/interrupt setting command and then specify whether to use the rising edge or falling edge of the strobe signal (INSTB) by WR2/D5 bit.

All the signals (the input value after passing through the filter) configured as input are latched by the transition of INSTB signal or can be latched by writing Simultaneous Input Latch Command (EAh). Simultaneous input latch data will be kept until next transition of INSTB signal or simultaneous input latch command (EAh) are written.

| Reference                           | Page |

|-------------------------------------|------|

| 5.1.9 Action Mode/Interrupt Setting | 30   |

| 5.3.11 Simultaneous Input Latch     | 37   |

If WR3/D1 bit is set to 1 by action mode/interrupt setting command, an interruption can be generated by the transition of INSTB signal.

[Note1] Depending on the level of the INSTB signal, data may be latched at the writing of action mode/interrupt setting command (C8h). For instance, when INSTB signal goes Hi and action mode/interrupt setting command (C8h) is written at the rising edge, data will also be latched at the time of the command writing.

[Note2] After latched by the transition of the INSTB signal, the next latch is not performed for a maximum of 4CLK cycles even though INSTB signal alters.

#### (2) Latch by Timer

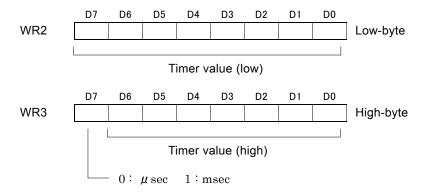

PIX132 is equipped with a built-in timer which can set within the range from  $1\mu$  sec to 32sec. All the input signals are simultaneously latched at the time-out of the timer. The timer can be operated by single activation command or continuous activation command which repeatedly operates until the CPU stops it. In continuous activation command, Input values are latched every time-out. The procedures for simultaneous input latch by the timer are shown as follows:

- $\bigcirc$  Set 1 to WR2/D3 bit by mode/interrupt setting command. Also set 1 to WR3/D0 bit if you need to generate the interrupt by the time-out.

- ② Set the timer value.

- 3 Activate the timer by single activation command or continuous activation command.

- ① Confirm the time-out by reading the activated timer value or the interrupt generation. When confirming by the interrupt generation, the user can validate the interruption from the timer by RR1/D0 bit. INTN signal will be released by reading RR1/D0 = 1.

| Reference                           | Page |

|-------------------------------------|------|

| 5.1.9 Action Mode/Interrupt Setting | 30   |

| 5.1.4 Timer Value Setting           | 28   |

| 5.3.1 Timer Single Activation       | 35   |

| 5.3.2 Timer Continuous Activation   | 35   |

| 5.2.3 Activated Timer Value Reading | 34   |

| 4.5 RR1 Register                    | 22   |

### (3) Reading Latched Input Value

Latched input value can be read from RR4, 5, 6 and 7 registers. At this time, RR4, 5, 6 and 7 registers should display "Latch Input", so write Read Register Display Selecting 3 Command (E7h) in advance to switch RR4, 5, 6 and 7 registers to a display "Latch Input".

| Reference                                  | Page |

|--------------------------------------------|------|

| 5.3.8 Read Register Display<br>Selecting 3 | 36   |

| 4.7 RR4,5,6,7 Register                     | 23   |

#### 2.3. Input Transition Trapping Function

This function is to trap the transition of input signals concerning all of the input signals.

#### (1) Setting

Configure whether to enable or disable the transition trapping function and specify the direction of the transition whether to trap the input value from 0 to 1 or from 1 to 0 for each input signal.

Enable/Disable can be set by PAB Input Transition Enabling Command or PCD Input Transition Enabling Command. And the direction of the transition can be set by PAB Input Transition Direction Command or PCD Input Transition Direction Command.

| Reference                            | Page |

|--------------------------------------|------|

| 5.1.5 PAB Input Transition Enabling  | 29   |

| Setting                              | 29   |

| 5.1.6 PCD Input Transition Enabling  | 29   |

| Setting                              | 29   |

| 5.1.7 PAB Input Transition Direction | 00   |

| Setting                              | 29   |

| 5.1.8 PCD Input Transition Direction | 20   |

| Setting                              | 30   |

## (2) Transition Trapping Behavior

Regarding the signal enabled by Input Transition Enabling Command, the transition trapping function is immediately operated. When an input value goes to the specified direction, the input transition becomes "1". This "1" is kept until the register corresponding to the input signal is read out even though the transition of the input signal occurs repeatedly.

#### (3) Reading Input Transition

Input transition information can be read from RR4, 5, 6, and 7 registers. At this time, RR4, 5, 6 and 7 registers should display "Input Transition", so write Read Register Display Selecting 5 Command(E9h) in advance to switch RR4, 5, 6 and 7 registers to a display "Input Transition".

|       | Reference                              | Page |

|-------|----------------------------------------|------|

| 5.3.1 | 0 Read Register Display<br>Selecting 5 | 37   |

| 4.7   | RR4,5,6,7 Register                     | 23   |

Input transition information will be cleared once read out.

# (4) Clearing Transition Information

Input transition information of each register is cleared by reading RR4~7 registers. Or it can be cleared for all the registers by command.

| Reference                          | Page |

|------------------------------------|------|

| 5.3.5 Input Transition Information | 35   |

| Clear                              | 33   |

[Note] This function is activated by clock (CLK) synchronization. Even without the filter, if the input transition occurs in less time than CLK cycle, it may fail to be trapped.

#### 2.4. Simultaneous Output Set

This function is to set all of the output signals in PA~PD ports simultaneously. To set the output simultaneously, there are three ways: strobe signal, commands and the timer. The user can specify which way is to be used by action mode/interrupt setting command.

#### (1) Simultaneous Output by Strobe Signal or Commands

To perform simultaneous output set by a strobe signal (OTSTB) or commands, set 1 to WR2/D0(Simultaneous Output 1) bit by action mode/interrupt setting command, and specify either the rising edge or falling edge of the strobe signal (OTSTB) by WR2/D4 bit.

If WR2/D0(Simultaneous Output 1) bit is set to 1 and action mode/interrupt setting command is written, then output signals cannot be changed by writing the output value in WR4, 5, 6 and 7 registers. Write the output value to all of WR4, 5, 6 and 7 registers and then make the strobe signal (OTSTB) change or write simultaneous output set command, all the output signals will be set simultaneously.

| Reference                           | Page |

|-------------------------------------|------|

| 5.1.9 Action Mode/Interrupt Setting | 30   |

| 5.3.12 Simultaneous Output Set      | 37   |

| 4.4 WR4,5,6,7 Register              | 22   |

If WR3/D2 bit is set to 1 by action mode/interrupt setting command, interrupt can be generated at the transition of the OTSTB signal.

#### (2) Simultaneous Output Set by Timer

PIX132 is equipped with a built-in timer which can set within the range from 1  $\mu$  sec to 32sec. Activating the timer, the user can simultaneously output the output values already written in WR4, 5, 6 and 7 registers at the time-out of the timer. There are two modes of timer behavior, single activation which works only once and continuous activation which repeatedly operates until the CPU stops it. In continuous activation, output values written in WR4, 5, 6 and 7 registers are simultaneously output every time-out. The procedures of simultaneous output set by the timer are shown as follows:

- ① Set 1 to WR2/D1 bit by mode/interrupt setting command. Also set 1 to WR3/D0 bit if you need to generate the interrupt by the time-out.

- ② Set the timer value.

- ③ Write output values in WR4, 5, 6 and 7 registers.

- Activate the timer by single activation command or continuous activation

- ⑤ Confirm the time-out by reading the activated timer value or the interrupt generation. Output signals are set at the time-out.

- $\odot$  With the interrupt generation, the user can validate the interruption from the timer by RR1/D0 bit. INTN signal will be released by reading RR1/D0 = 1

- the timer by RR1/D0 bit. INTN signal will be released by reading RR1/D0 = 1.

When the timer is activated in continuous activation, write next output values in WR4 5 6.

- When the timer is activated in continuous activation, write next output values in WR4, 5, 6 and 7 registers and then repeat

5 to 6.

## Notes on Simultaneous Output Set:

## Output Port Capacitance Load

Please do not set the capacitance load over 50pF per output port to all the outputs simultaneously, as an operation error may occur. In such a case, place the driver IC after the output port.

## Preventive measures for Simultaneous Switching

In a customer system, when the user tries to control switching on/off of a large current in the back step of this IC using the simultaneous output set function, it is necessary to take preventive measures that minimize the voltage fluctuation of GND/Power or Cross-Talk between the signals which are generated by simultaneous switching of a large current.

## Delay in Port PA, PD

To avoid malfunction by simultaneous switching in the IC, outputs of ports PA, PD are delayed about 7nsec (VDD=5V typ. value) from those of ports PB, PC. See section 8.2.9.

## 2.5. Bit Control Output

This function is to set an output signal by a single bit. When the user tries to set a specified output signal to Low level, write the designation number for the signal to WR0 register, then the signal will be set to Low. And write the

|     | Reference    | Page |

|-----|--------------|------|

| 4.1 | WR0 Register | 20   |

| 4.2 | WR1 Register | 21   |

designation number for the signal to WR1 register, then the corresponding signal will be set to Hi.

| 5.1.9 Action Mode/Interrupt Setting | 30 |

|-------------------------------------|----|

| 5.1.4 Timer Value Setting           | 28 |

| 5.3.1 Timer Single Activation       | 35 |

| 5.3.2 Timer Continuous Activation   | 35 |

| 5.2.3 Activated Timer Value Reading | 34 |

| 4.4 WR4,5,6,7 Register              | 22 |

|                                     |    |

Reference

Page

#### 2.6. Built-in Timer

PIX132 is equipped with a built-in timer which can set within the range from  $1 \mu$  sec to 32sec. The following three operations can be performed at the time-out of the timer. Please refer to each section.

Simultaneous Input Latch

Simultaneous Output Set

Interrupt Generation

Section 2.4

Section 2.7

Procedures to activate the timer are shown as follows:

- ① Set the timer value.

- ② If you need to generate the interrupt by the time-out, set 1 to WR3/D0 bit by mode/interrupt setting command.

- 3 Activate the timer by single activation command or continuous activation command.

- To stop the single activated timer, write Timer Stop Command. And to stop the continuous activated timer, write Timer Stop Command or Timer Cycle Stop Command.

| Reference                           | Page |

|-------------------------------------|------|

| 5.1.9 Action Mode/Interrupt Setting | 30   |

| 5.1.4 Timer Value Setting           | 28   |

| 5.3.1 Timer Single Activation       | 35   |

| 5.3.2 Timer Continuous Activation   | 35   |

| 5.3.3 Timer Stop                    | 35   |

| 5.3.4 Timer Cycle Stop              | 35   |

| 5.2.3 Activated Timer Counter Value | 34   |

| Reading                             | 54   |

|                                     |      |

## 2.7. Interrupt Generation

This IC has an interrupt output signal (INTN) to the CPU. The INTN signal is the open drain output so that it is necessary to pull up to the VDD through resistance. Interrupt can be generated by the following four operations. To enable each interrupt generation, specify it by action mode/interrupt setting command.

- · Time-out of the timer

- Transition of INSTB signal at the simultaneous input latch

- · Transition of OTSTB signal at the simultaneous output set

- Input Transition

| Reference                           | Page |

|-------------------------------------|------|

| 5.1.9 Action Mode/Interrupt Setting | 30   |

|                                     |      |

## 2.8. Status at Reset

At resetting, each configurable operation in slave mode of this IC is shown as follows:

| Operation                              | Status at Reset                            | Related Commands              |

|----------------------------------------|--------------------------------------------|-------------------------------|

| Port PA~PD Input/Output                | All the signals are Input.                 | Designation of Input/Output   |

| Port PA~PD Input Logic                 | All the signals are 0. (Hi to 1)           | and Logical Setting.          |

| Port PA~PD Filter Designation          | All the signals are without filter.        | Input Filter Designation      |

| Filter Time Constant 1, 2, 3           | All of 1, 2, 3 is 0. (Delay Time 1 $\mu$ ) | Filter Time Constant Setting  |

| Timer Value                            | 0                                          | Timer Value Setting           |

| PAB, PCD Input Transition              | All the signals are disabled.              | PAB, PCD Input Transition     |

| Enabling/Disabling                     |                                            | Enabling Setting              |

| PAB, PCD Input Transition Direction    | All the signals are 0. (Transition of      | PAB, PCD Input Transition     |

|                                        | input value from 0 to 1.)                  | Direction Setting             |

| Simultaneous Output 1                  | Disable                                    |                               |

| (Strobe/Commands)                      |                                            |                               |

| Simultaneous Output 2 (Timer)          | Disable                                    |                               |

| Simultaneous Input Latch 1             | Disable                                    |                               |

| (Strobe/Commands)                      |                                            |                               |

| Simultaneous Input Latch 2(Timer)      | Disable                                    |                               |

| OTSTB Direction                        | 0 (the rising edge)                        | Action Mode/Interrupt Setting |

| INSTB Direction                        | 0 (the rising edge)                        | Action Mode/interrupt Setting |

| Interrupt by Timer                     | Disable                                    |                               |

| Interrupt by Simultaneous Input Latch  | Disable                                    |                               |

| INSTB Signal                           |                                            |                               |

| Interrupt by Simultaneous Output OTSTB | Disable                                    |                               |

| Signal                                 |                                            |                               |

| Interrupt by Input Transition          | Disable                                    |                               |

| -                                      | •                                          | •                             |

# 3. Pin Assignments and Signal Description

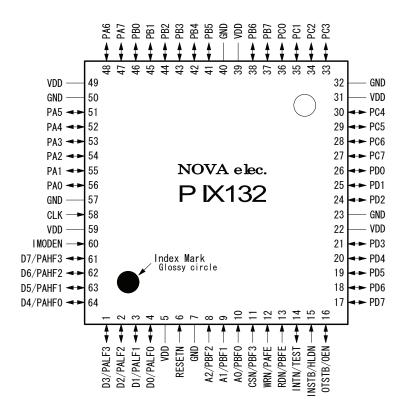

# 3.1. Pin Assignments

- 64 pin TQFP package, external package: 12×12mm, lead pitch: 0.5mm, lead free

- See Chapter 9 for the package dimensions.

# 3.2. Signal Description

See section 3.3 for Input/Output in the table.

|             | Pin    |                  | Signal Description                                                                                                                                                                                                                                                     |                                                                                                                                                                                      |

|-------------|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name | Number | Input/Output     | Slave Mode                                                                                                                                                                                                                                                             | Independent Mode                                                                                                                                                                     |

| CLK         | 58     | Input A          | Clock: clock signal for internal syr<br>The standard frequency is 16MHz<br>timer value is based upon. If the<br>the filter time constant or timer va                                                                                                                   | nchronous circuits of PIX132. , which the filter time constant or frequency setting is not 16MHz,                                                                                    |

| D0/PALF0    | 4      | Bi-directional A | D0 $\sim$ D7 Data Bus: 3-state                                                                                                                                                                                                                                         | PALF0~3: signals for PA lower                                                                                                                                                        |

| D1/PALF1    | 3      | Bi-directional A | bi-directional 8-bit data bus,                                                                                                                                                                                                                                         | 4-bit (PA0~3) inputs to set the                                                                                                                                                      |

| D2/PALF2    | 2      | Bi-directional A | used in conjunction with system                                                                                                                                                                                                                                        | time constant of an integral                                                                                                                                                         |

| D3/PALF3    | 1      | Bi-directional A | data bus. D7 is the highest signal and D0 is the lowest signal. Low is 0 and Hi is 1.                                                                                                                                                                                  | filter. PALF3 is the highest signal and PALF0 is the lowest signal. Low is 0 and Hi is 1.                                                                                            |

| D4/PAHF0    | 64     | Bi-directional A | When CSN is Low and RDN is                                                                                                                                                                                                                                             | PAHF0 $\sim$ 3: signals for PA                                                                                                                                                       |

| D5/PAHF1    | 63     | Bi-directional A | Low, these signals are for                                                                                                                                                                                                                                             | upper 4-bit (PA4~7) inputs to                                                                                                                                                        |

| D6/PAHF2    | 62     | Bi-directional A | outputting.                                                                                                                                                                                                                                                            | set of the time constant of an                                                                                                                                                       |

| D7/PAHF3    | 61     | Bi-directional A |                                                                                                                                                                                                                                                                        | integral filter. PAHF3 is the highest signal and PAHF0 is the lowest signal. Low is 0 and Hi is 1.                                                                                   |

| A0/PBF0     | 10     | Input A          | A0 $\sim$ A2 Address: address                                                                                                                                                                                                                                          | PBF0~3: signals for port PB                                                                                                                                                          |

| A1/PBF1     | 9      | Input A          | signals for host CPU to access                                                                                                                                                                                                                                         | (PB0~7) inputs to set the time                                                                                                                                                       |

| A2/PBF2     | 8      | Input A          | the read /write registers. A2 is constant of an integral the highest signal and A0 is the PBF3 is the highest signal                                                                                                                                                   | constant of an integral filter. PBF3 is the highest signal and PBF0 is the lowest signal. Low is 0 and Hi is 1.                                                                      |

| CSN/PBF3    | 11     | Input A          | Chip Select: input signal for selecting PIX132 as I/O device. Set Low level for data reading and writing.                                                                                                                                                              | [Note] Please note that the pins for PBF3~0 are not in sequence.                                                                                                                     |

| WRN/PAFE    | 12     | Input A          | Write Strobe: set Low when data is written in the write registers. When WRN is Low, CSN and A2~A0 must be valid. When data PA Filter Enable: signal enable the integral filter of input. Hi is enable and Lo disable. When it is disable                               | PA Filter Enable: signal to enable the integral filter of PA input. Hi is enable and Low is disable. When it is disabled, PA input is directly output to port PC without the filter. |

| RDN/PBFE    | 13     | Input A          | Read Strobe: set Low when data is read out from the read register. When CSN is set to Low and RDN is set to Low, the data of the read register selected by A2~A0 address signal is output to the data bus during RDN Low.                                              | PB Filter Enable: signal to enable the integral filter of PB input. Hi is enable and Low is disable. When it is disabled, PB input is directly output to port PD without the filter. |

| RESETN      | 6      | Input A          | Reset: reset (initialize) signal for PIX132. Setting to Low, PIX132 will be reset. Power-on reset by RESETN signal is necessary. After PIX132 has been reset, all of the ports of PA~PD will be input. And all of mode settings are also initialized. See section 2.8. | Reset: reset (initialize) signal for PIX132. When RESETN signal is Low, outputs of port PC, PD will be Low regardless of input signals of port PA, PB.                               |

|                | Pin                                 |                                    | Signal Description                                                                                                                                                                                      |                                                                                                                                                                                     |

|----------------|-------------------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name    | Number                              | Input/Output                       | Slave Mode                                                                                                                                                                                              | Independent Mode                                                                                                                                                                    |

| INTN/TEST      | 14                                  | Bi-directional A                   | Interrupt: output signal of interrupt request for host CPU. If the interrupt is generated by any interrupt factor, INTN will become Low. After the interrupt is released, it will return to Hi-Z level. | Test: input signal for testing the internal circuits. When in independent mode (IMODEN=Low), this signal must be connected to GND, or the internal test circuits will be activated. |

| IMODEN         | 60                                  | Input A                            | Independent Mode: Set Low (cor<br>operated in independent mode. An<br>PIX132 is operated in CPU slave r                                                                                                 | nd set Hi (connect to VDD) when                                                                                                                                                     |

| PA7~PA0        | 47,48,51,<br>52,<br>53,54,55,<br>56 | Bi-directional A                   | Port A: PA, 8-bit I/O ports.  Upper 4-bit and lower 4-bit can be independently configured input/output by mode setting.                                                                                 | PA, 8-bit input ports. These are for input only.                                                                                                                                    |

| PB7~PB0        | 37,38,41,<br>42,<br>43,44,45,<br>46 | Bi-directional A                   | Port B: PB, 8-bit I/O ports.  Upper 4-bit and lower 4-bit can be independently configured input/output by mode setting.                                                                                 | PB, 8-bit input ports These are for input only.                                                                                                                                     |

| PC7~PC0        | 27,28,29,<br>30,<br>33,34,35,<br>36 | Bi-directional A                   | Port C: PC, 8-bit I/O ports. Upper 4-bit and lower 4-bit can be independently configured input/output by mode setting.                                                                                  | PC, 8-bit output ports. PA input signal is output through an integral filter.                                                                                                       |

| PD7~PD0        | 17,18,19,<br>20,<br>21,24,25,<br>26 | Bi-directional A                   | Port D: PD, 8-bit I/O ports. Upper 4-bit and lower 4-bit can be independently configured input/output by mode setting.                                                                                  | PD, 8-bit output ports. PB input signal is output through an integral filter.                                                                                                       |

| INSTB/HLD<br>N | 15                                  | Input A                            | Input Latch Strobe: strobe pulse to latch PA~PD inputs. Mode setting is necessary to function this.                                                                                                     | Hold: hold the output of ports PC, PD. This signal is low level to hold the port PC, PD.                                                                                            |

| OTSTB/OEN      | 16                                  | Bi-directional B (uses input only) | Output Latch Strobe: strobe pulse input for PA~PD outputs to simultaneously output. Mode setting is necessary to function this.                                                                         | Output Enable: signal to enable PC, PD output ports. When this signal is low, PC, PD output signals will be enabled. And when Hi, they wll be high impedance.                       |

| VDD            | 5,22,31,<br>39,49,59                |                                    | +5V(or +3.3V) Power Terminal. All of the 6 pins must be connect substrate.                                                                                                                              | ted to the power pattern on the                                                                                                                                                     |

| GND            | 7,23,32,<br>40,50,57                |                                    | Ground 0V Terminal.  All of 6 pins must be connected substrate.                                                                                                                                         | I to the ground pattern on the                                                                                                                                                      |

# 3.3. Input/ Output Circuit

| Input A        | More than $10k\Omega$ ~hundreds of kilo impedance is for internal impedance, which can pull up the  |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------|--|--|--|

|                | VDD to the TTL Level input of a Smith trigger.                                                      |  |  |  |

|                | CMOS and TTL can be connected.                                                                      |  |  |  |

|                | The user should open or pull up to VDD if the input is not used.                                    |  |  |  |

| Bi-directional | Input side is TTL Smith trigger, which is high impedance because it is not pulled up with high      |  |  |  |

| Α              | resistance in the IC. Pull up signals, which are not used, with high resistance to VDD or pull      |  |  |  |

|                | down to GND. Concerning data signals (D7~D0), the user should pull up the data bus with high        |  |  |  |

|                | resistance for signal line not to attain high impedance.                                            |  |  |  |

|                | Output side is CMOS level output, 8mA driving buffer at VDD=5V (High level output current           |  |  |  |

|                | IOH=-8mA, VOH=2.4Vmin, Low level output current IOL=8mA, VOL=0.4Vmax) and 4mA driving               |  |  |  |

|                | buffer at VDD=3.3V (Hi level output current IOH=-4mA, VOH=2.4Vmin, Low level output current         |  |  |  |

|                | IOL=4mA, VOL=0.44Vmax).                                                                             |  |  |  |

| Bi-directional | The same circuit as bi-directional A but uses input only. Input side is TTL Smith trigger, which is |  |  |  |

| В              | high impedance because it is not pulled up with high registance in the IC. When IMODEN is           |  |  |  |

|                | Low (independent mode), INTN/TEST signal must be connected to GND, or the internal test             |  |  |  |

|                | circuit will be activated and the OTSTB/OEN signal will be output.                                  |  |  |  |

# 3.4. Notes for Design Circuitry

# Processing of GND, VDD Terminals

Make sure that all of GND and VDD terminals are each connected to the ground pattern and the power pattern on the substrate.

# **De-coupling Capacitor**

Please connect VDD and GND with two to four De-coupling capacitors (about 0.1  $\mu$  F).

# 4. Register

This chapter indicates to the user how to access all the registers in PIX132, and what the mapping addresses are of these registers.

Both read and write registers have eight registers respectively and each register consists of 8-bit.

#### Writing/ Reading Operation

In order to write the data of the write register, select the register by  $A2\sim A0$  signal, if CSN signal is Low and WRN signal is set from Low to Hi, values of the data bus (D7 $\sim$ D0) will be written in the selected register. Also in order to read the data of the read register, select the register by  $A2\sim A0$  signal, if CSN signal is Low and RDN signal is set to Low, values of the read register will be output to the data bus (D7 $\sim$ D0). For more details on read/ write timing, please refer to chapter 8.4.2.

## ■ Write Register

| Α  | Address |    | Cumbal | Function                                 |  |

|----|---------|----|--------|------------------------------------------|--|

| A2 | A1      | A0 | Symbol | i unction                                |  |

| 0  | 0       | 0  | WR0    | Command Execution, Bit Control Output: 0 |  |

| 0  | 0       | 1  | WR1    | Bit Control Output: 1                    |  |

| 0  | 1       | 0  | WR2    | Data Writing (Lower)                     |  |

| 0  | 1       | 1  | WR3    | Data Writing (Upper)                     |  |

| 1  | 0       | 0  | WR4    | Port PA Output Value Setting             |  |

| 1  | 0       | 1  | WR5    | Port PB Output Value Setting             |  |

| 1  | 1       | 0  | WR6    | Port PC Output Value Setting             |  |

| 1  | 1       | 1  | WR7    | Port PD Output Value Setting             |  |

# Read Register

| Α  | ddres | s  | Symbol | Function                                                                  |

|----|-------|----|--------|---------------------------------------------------------------------------|

| A2 | A1    | Α0 | Symbol | Function                                                                  |

| 0  | 0     | 0  | RR0    | Not used                                                                  |

| 0  | 0     | 1  | RR1    | Display of Interrupt Request Factor                                       |

| 0  | 1     | 0  | RR2    | Display of Reading Data (Lower)                                           |

| 0  | 1     | 1  | RR3    | Display of Reading Data (Upper)                                           |

| 1  | 0     | 0  | RR4    | Port PA Display of Real-time Input, Latch Input, Output, Input Transition |

| 1  | 0     | 1  | RR5    | Port PB Display of Real-time Input, Latch Input, Output, Input Transition |

| 1  | 1     | 0  | RR6    | Port PC Display of Real-time Input, Latch Input, Output, Input Transition |

| 1  | 1     | 1  | RR7    | Port PD Display of Real-time Input, Latch Input, Output, Input Transition |

# 4.1. WR0 Register ----- Command Execution / Bit Control Output: 0

WR0 Register is used for the following two functions:

#### ① Command Execution

Writing a value more than C0 (hex) to WR0 register, PIX132 takes it as a command and then the corresponding command is executed. Please refer to chapter 5 for command execution.

## ② Bit Control Output: 0

The function for only one output signal to be set to low by writing the number corresponding to the output signal to WR0 register. Write the signal designation number corresponding to the signal shown in the table to D4~D0 of WR0 register, and the corresponding output signal will be low.

[Note] Bit control output: 0 is disabled when the simultaneous output is set (D0 or D1 by C8 command.).

|     | D7 | D6 | D5 | D4    | D3     | D2      | D1    | D0   |                       |

|-----|----|----|----|-------|--------|---------|-------|------|-----------------------|

| WR0 | 0  | 0  | 0  |       |        |         |       |      | Bit Control Output: 0 |

|     |    |    | L  |       |        |         |       |      | (Output: Low)         |

|     |    |    |    | Signa | al Des | ignatio | n Nun | nber |                       |

| Signal Designation<br>Number<br>(HEX) | Signal<br>Name | Pin Number | Signal Designation<br>Number<br>(HEX) | Signal<br>Name | Pin Number |

|---------------------------------------|----------------|------------|---------------------------------------|----------------|------------|

| 00                                    | PA0            | 56         | 10                                    | PC0            | 36         |

| 01                                    | PA1            | 55         | 11                                    | PC1            | 35         |

| 02                                    | PA2            | 54         | 12                                    | PC2            | 34         |

| 03                                    | PA3            | 53         | 13                                    | PC3            | 33         |

| 04                                    | PA4            | 52         | 14                                    | PC4            | 30         |

| 05                                    | PA5            | 51         | 15                                    | PC5            | 29         |

| 06                                    | PA6            | 48         | 16                                    | PC6            | 28         |

| 07                                    | PA7            | 47         | 17                                    | PC7            | 27         |

| 08                                    | PB0            | 46         | 18                                    | PD0            | 26         |

| 09                                    | PB1            | 45         | 19                                    | PD1            | 25         |

| 0A                                    | PB2            | 44         | 1A                                    | PD2            | 24         |

| 0B                                    | PB3            | 43         | 1B                                    | PD3            | 21         |

| 0C                                    | PB4            | 42         | 1C                                    | PD4            | 20         |

| 0D                                    | PB5            | 41         | 1D                                    | PD5            | 19         |

| 0E                                    | PB6            | 38         | 1E                                    | PD6            | 18         |

| 0F                                    | PB7            | 37         | 1F                                    | PD7            | 17         |

- It will be disabled when the designation of the signal is not defined as output.

- [Note] Set 0 to D7~5 bits of WR0 register, or unexpected commands may be executed.

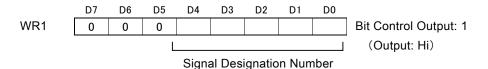

## 4.2. WR1 Register ----- Bit Control Output: 1

The function for only one output signal to be set to Hi by writing the number corresponding to the output signal to WR1 register. Write the signal designation number corresponding to the signal shown in the table in section 4.1. to D4 $\sim$ D0 of WR1 register, and the corresponding output signal will be Hi.

[Note] Bit control output: 1 is disabled when simultaneous output is set (D0 or D1 by C8 command.).

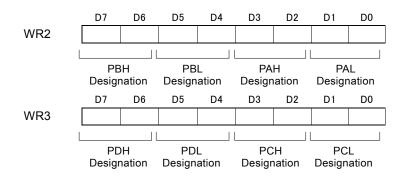

### 4.3. WR2,3 Register ----- Data Writing

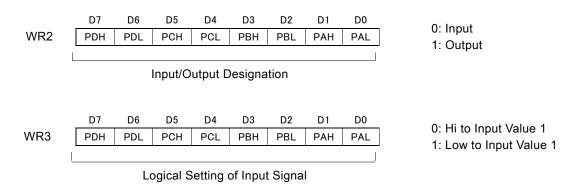

WR2, 3 registers are used to set the data of commands for data writing. Writing the command code to WR0 register after setting the data to WR2, 3 registers, the contents of WR2, 3 registers will be taken to the IC. When the data is a 2-byte length, set low-byte data to WR2 register and high-byte data to WR3 register. When the data is a 1-byte length, only set to WR2 register with no need to set 0 to WR3 register.

|     | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |                          |

|-----|----|----|----|----|----|----|----|----|--------------------------|

| WR2 |    |    |    |    |    |    |    |    | Low-byte of Writing Data |

|     | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |                           |

|-----|----|----|----|----|----|----|----|----|---------------------------|

| WR3 |    |    |    |    |    |    |    |    | High-byte of Writing Data |

## 4.4. WR4,5,6,7 Register ---- Port Output Value Setting

These registers are configurable output values of each port PA, PB, PC and PD. Low can be set to 0 to the corresponding bit of each signal and Hi to 1 as well. If the user only sets each half of the port to output mode, either value (1 or 0) can be set to the rest of signals configured as input mode. They are ignored.

|     | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |                              |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|------------------------------|

| WR4 | PA7 | PA6 | PA5 | PA4 | PA3 | PA2 | PA1 | PA0 | Port PA Output Value Setting |

|     |     |     |     |     |     |     |     |     | 0:Low 1:Hi                   |

|     | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |                              |

| WR5 | PB7 | PB6 | PB5 | PB4 | PB3 | PB2 | PB1 | PB0 | Port PB Output Value Setting |

|     | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |                              |

| WR6 | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 | Port PC Output Value Setting |

|     |     |     |     |     |     |     |     |     |                              |

|     | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |                              |

| WR7 | PD7 | PD6 | PD5 | PD4 | PD3 | PD2 | PD1 | PD0 | Port PD Output Value Setting |

- If the user enables simultaneous output 1, 2 (See action mode/interrupt setting command (C8h)), output does not alter immediately after writing the value to WR4, 5, 6 and 7 registers.

- When the user does not set the input/output of each signal to output mode by input/output designation command (C0h), data will not output by writing to these registers.

# 4.5. RR1 Register ----- Display of Interrupt Request Factor

D7

Displays the interrupt request factor (except for input transition). 1 indicates that is the interrupt request factor.

|    |     | RR1   | 0       | 0      | 0       | 0     | 0      | OTS     | INS | TIM | 1: Interrupt Request                         |

|----|-----|-------|---------|--------|---------|-------|--------|---------|-----|-----|----------------------------------------------|

| D0 | TIM |       |         |        |         |       |        | ,       |     |     | setting value).<br>t = at the setting value. |

| D1 | INS | indic | cates t | he tra | nsition | of IN | STB si | gnal.   |     |     |                                              |

| D2 | OTS | indic | cates t | he tra | nsition | of OT | STB    | signal. |     |     |                                              |

D3

D2

D1

D0

- To generate the interrupt, the interrupt factor which is needed must be enabled by action mode/interrupt setting command (C8h) in advance.

- · Once the CPU reads out, all the bits of RR1 register will be cleared.

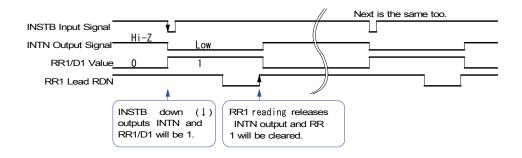

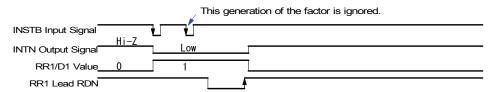

#### ■ Common Interrupt Operation

When the interrupt factor enabled by action mode/interrupt setting command is generated, the INTN signal will go from Hi-Z to Low level and 1 will be set to the proper bit of RR1 register. And after reading RR1 register during interrupt processing routine in the CPU, the INTN output signal will return to Hi-Z and all the bits of RR1 register will be cleared to 0.

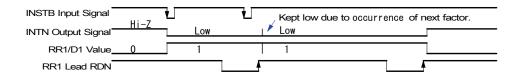

#### ■ In the case when next factor has been generated while reading RR1 register.

When the interrupt generation of each factor and the timing of reading from the CPU overlaps, the interrupt generation will be held internally until reading is finished, so PIX132 does not miss next interrupt generation by reading.

■ In the case when next factor has been generated ahead of reading RR1 register after an interruption occurred. When the same factor has been generated again ahead of reading RR1 after an interruption occurs, this interrupt generation is ignored.

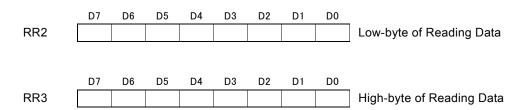

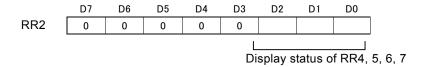

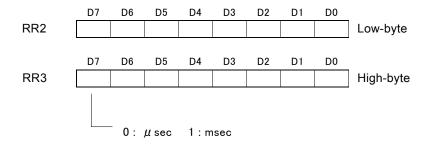

#### 4.6. RR2,3 Register ----- Display of Reading Data

RR2, 3 resigsters are used to set the data of commands for reading data. Writing the command code to WR0 register, the data corresponding to the command will be set from the internal circuits to RR2, 3 registers. When the data is a 2-byte length, low-byte data will be set to RR2 register and high-byte data will be set to RR3 register. When the data is a 1-byte length, data will be set to RR2 register and 0 will be set to RR3 register.

### 4.7. RR4,5,6,7 Register ---- Display of Real-time Input/Latch Input/Output/Input Transition

RR4, 5, 6 and 7 registers are used to display input values of ports, PA, PB, PC and PD respectively. Each register corresponds to RR4:PA[7:0], RR5:PB[7:0], RR6:PC[7:0] and RR7:PD[7:0].

|     | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |         |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|---------|

| RR4 | PA7 | PA6 | PA5 | PA4 | PA3 | PA2 | PA1 | PA0 | Port PA |

|     |     |     |     |     |     |     |     |     |         |

|     | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |         |

| RR5 | PB7 | PB6 | PB5 | PB4 | PB3 | PB2 | PB1 | PB0 | Port PB |

|     |     |     |     |     |     |     |     |     |         |

|     | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |         |

| RR6 | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 | Port PC |

|     |     |     |     |     |     |     |     |     |         |

|     | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |         |

| RR7 | PD7 | PD6 | PD5 | PD4 | PD3 | PD2 | PD1 | PD0 | Port PD |

|     |     |     |     |     |     |     |     |     |         |

RR4, 5, 6 and 7 registers also display not only real-time input (current input value) but latch input, input transition and current output value. This displayed information can be switched by E5 to E9h commands.

| Displayed Information | Contents                                        | Command for       | Bit (1, 0) Description |  |  |  |

|-----------------------|-------------------------------------------------|-------------------|------------------------|--|--|--|

|                       |                                                 | Selecting Display |                        |  |  |  |

| Real-time Input       | Displays input value which passed an            | E6                | Depends on input logic |  |  |  |

|                       | integral filter.                                |                   | setting.               |  |  |  |

| Latch Input           | Displays latched input value which passed       | E7                | Depends on input logic |  |  |  |

|                       | an integral filter. Note1                       | <i>□ 1</i>        | setting.               |  |  |  |

| Output                | Displays the status of the output signal        | E8                | 0:Low level            |  |  |  |

|                       | currently set.                                  | □ □ □             | 1:Hi level             |  |  |  |

| Input Transition      | Displays input transition. Note2                |                   | 0:No transition        |  |  |  |

|                       | Information of input transition will be cleared | E9                | 1: Transition occured  |  |  |  |

|                       | once it is read out.                            |                   |                        |  |  |  |

| Real-time Input +     | Displays real-time input when the signal is     |                   | See above.             |  |  |  |

| Output                | set to input mode and displays output value     | E5                |                        |  |  |  |

|                       | when the signal is set to output mode.          |                   |                        |  |  |  |

[Note1] Latch is performed by any of the three, external signal (INSTB), command (EAh) or the timer.

[Note2] It is necessary to enable input transition trapping and set the direction of transition in advance.

The user does not need to write commands for selecting display every reading of the input value. Once the commands for selecting display are written, they are valid until next commands for selecting display are written.

The user can confirm the current displayed information of each RR4, 5, 6 and 7 registers. Writing commands for reading data (D9h) of read register display status, the user can read the current selection from RR2 register. For more details, see chapter 5.2.2.

# 5. Commands

Commands for PIX132 are classified into three groups: commands for data writing, commands for reading data and other commands.

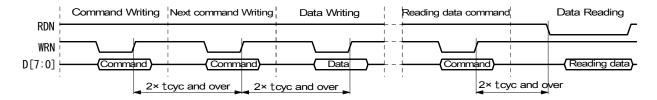

Commands for data writing can be performed by writing the command code to WR0 after writing the data in WR2 and WR3. WR2 is for low-byte data and WR3 is for high-byte data. If the data is a 1-byte length, the user only writes in WR2 and no need to write 0 in WR3.

Commands for reading data can be performed by writing the command code to WR0, which sets reading data to RR2, 3. If the data is a 1-byte length, the data will be set to RR2 register and RR3 (high-byte) will be 0.

Other commands can be performed by writing the command code to WR0.